要实现高效计算,可以从三个层面入手:提升计算单元的性能、采用更优的计算方法以及降低网络传输的延迟。本文将聚焦于网络设备,探讨如何通过优化交换机来减少转发延迟。

主流的L3交换机硬件结构包括专用集成电路(ASIC)、端口子系统、物理层子系统(PHY)、CPU、复杂可编程逻辑设备(CPLD)和事件处理器。其中,ASIC负责高速报文转发,PHY将链路层设备连接到物理介质,端口子系统管理端口配置,CPU则类似于一个小型服务器,处理复杂任务。

交换机的核心功能是高效处理海量报文,这一功能主要由ASIC和CPU协同完成。ASIC负责二三层转发,内部包含MAC地址表和三层转发表;CPU则维护软件表项,配置ASIC的硬件表项,并在必要时进行软件三层转发。两者相辅相成,确保了交换机的大容量转发能力。

然而,传统交换机在某些特定场景下难以满足极致低时延的需求。为此,IB和FC交换机应运而生。IB交换机基于Infiniband标准,支持RDMA技术,能直接访问远程内存,减少CPU开销和传输时延;FC交换机则基于光纤通道协议,适用于高性能存储网络。尽管这两种交换机在低时延方面表现出色,但其高昂的成本和复杂的运维限制了广泛应用。

可编程交换机则提供了另一种选择。基于FPGA开发的可编程交换机具有高度的灵活性和可编程性,可根据具体需求进行配置和优化,适用于多样化的网络环境和应用场景。

在选择交换机时,企业需综合考虑时延、稳定性、成本和可管理性等因素。低时延固然重要,但过高的投入未必划算。例如,在金融高频交易场景中,低时延至关重要,值得高投入;而在其他场景,低时延需求可能逐渐弱化,过度投资反而带来风险。

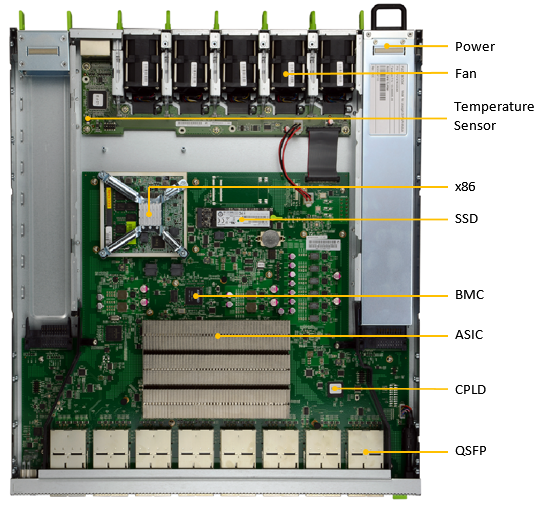

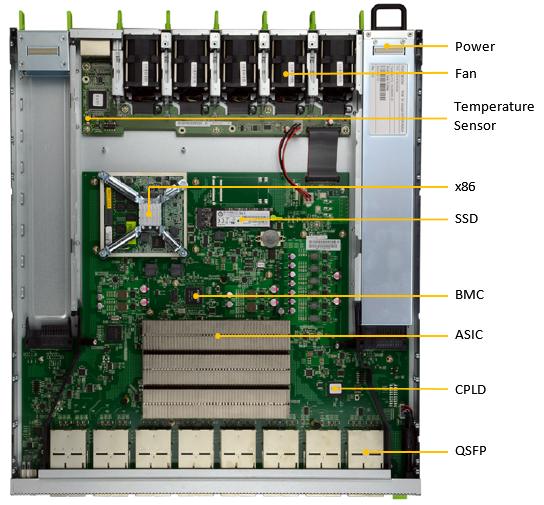

因此,网络规划和设计应基于实际需求,权衡性能与成本,合理配置低时延交换机,以实现最优的网络架构和投资回报。在数字化转型过程中,企业和组织将大量业务流程和数据存储在云端。 这些数据和流程需要通过计算进行分析和执行。 通过提高计算效率,企业可以更快地流转、分析和决策,这可以在一定程度上提高生产力。 要实现高效计算,这个目标可以分解为三个方向:提高计算单元的计算能力、采用更高效的计算方法、降低网络传输延迟。考虑到深入细节可能过于冗长,本文将从网络设备的角度简要讨论转发延迟问题。 主流交换机结构 我们先从当前主流的 L3交换机 硬件来剖析,包含硬件有:交换机专用集成电路(ASIC)、端口子系统、物理层子系统(PHY)、CPU、复杂可编程逻辑设备(CPLD)和事件处理器:

其中一些关键硬件的简介:

交换机ASIC Application Specific Integrated Circuit(专用集成电路),用于报文高速转发。

PHY(物理层子系统)负责将链路层设备(例如ASIC)连接到物理介质(例如光纤),并将链路上的模拟信号转换为数字化的以太网帧。

端口子系统负责读取端口配置,检测已安装端口的类型,初始化端口以及为端口提供与PHY交互的接口。

CPU板在交换机中存在一个运行微服务器的CPU板。CPU板非常类似于商业服务器,包含商业x86 CPU、RAM和存储介质。

其它板管理器交换机将各种繁杂功能从CPU和ASIC卸载到其它各种组件,以提高整体系统性能。例如:复杂编辑器件(CPLD)和基板管理控制器(BMC)。

交换机的转发处理

交换机的核心特性是能高效的处理海量报文,实现这一点的正是ASIC+CPU两大模块:

ASIC:完成主要的二三层转发功能,内部包含用于二层转发的MAC地址表以及用于IP转发的三层转发表;

CPU:用于转发的控制,主要维护一些软件表项(包括软件路由表、软件ARP表等等),并根据软件表项的转发信息来配置ASIC的硬件三层转发表。当然,CPU本身也可以能完成软件三层转发。

从三层交换机的结构和各部分作用可以看出,真正决定高速交换转发的是ASIC中的二三层硬件表项,而ASIC的硬件表项来源于CPU维护的软件表项,两者的相辅相成实现了交换机大容量转发。

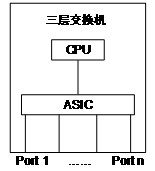

基于以上原理解释,可以将交换机内部抽象为下图:

其中一些关键硬件的简介:

交换机ASIC Application Specific Integrated Circuit(专用集成电路),用于报文高速转发。

PHY(物理层子系统)负责将链路层设备(例如ASIC)连接到物理介质(例如光纤),并将链路上的模拟信号转换为数字化的以太网帧。

端口子系统负责读取端口配置,检测已安装端口的类型,初始化端口以及为端口提供与PHY交互的接口。

CPU板在交换机中存在一个运行微服务器的CPU板。CPU板非常类似于商业服务器,包含商业x86 CPU、RAM和存储介质。

其它板管理器交换机将各种繁杂功能从CPU和ASIC卸载到其它各种组件,以提高整体系统性能。例如:复杂编辑器件(CPLD)和基板管理控制器(BMC)。

交换机的转发处理

交换机的核心特性是能高效的处理海量报文,实现这一点的正是ASIC+CPU两大模块:

ASIC:完成主要的二三层转发功能,内部包含用于二层转发的MAC地址表以及用于IP转发的三层转发表;

CPU:用于转发的控制,主要维护一些软件表项(包括软件路由表、软件ARP表等等),并根据软件表项的转发信息来配置ASIC的硬件三层转发表。当然,CPU本身也可以能完成软件三层转发。

从三层交换机的结构和各部分作用可以看出,真正决定高速交换转发的是ASIC中的二三层硬件表项,而ASIC的硬件表项来源于CPU维护的软件表项,两者的相辅相成实现了交换机大容量转发。

基于以上原理解释,可以将交换机内部抽象为下图:

来模拟一下报文转发情况,当普通数据流发送到设备port1时,ASIC芯片将直接通过匹配硬件表项来决定转发行为。而当信令、协议报文转发至port1时,ASIC芯片不能处理此类报文,将会把报文上送至CPU,由CPU统一处理, 当CPU处理过量报文时设备将不能稳定运行,所以在CPU设置处理上限及队列是软件设计的必要考虑。

更快的可能性

CPU+ASIC芯片的组合交换机可以满足绝大多数场景的需求,但在某些特定场景中,用户对于低时延交换机的要求是苛刻的,当前ASIC芯片多为商用(定制化设计),内部实现流程不透明;功能和算法在制造之前就被固定下来,转发查表架构固定,不能根据应用场景和具体科研需求进行更改,因此难以实现细分场景的极致需求。

IB/FC交换机

为实现极致低时延的网络诉求,IB及FC技术标准被定义。

共同点:

IB/FC交换机都可以执行Cut-through转发方式,即在接收到数据包的前半部分时就开始进行转发,而不必等到整个数据包接收完成。这种转发方式可以实现非常低的延迟,但可能会带来一些错误。

都采用专用的硬件转发引擎和硬件加速技术来减少时延。

FC的其他特点:基于光纤通道(FC)协议的低延时和低误码,支持点到点结构、环行拓扑结构和交换拓扑结构,通常提供4Gbps、8Gbps、16Gbps等带宽,适用于对性能要求较高的存储网络(SAN)应用场景。通过FC交换机将各个目标设备进行连接,以及FC交换机之间的级联,可以扩大存储区域网络的规模。 光纤通道传输速率高,延时低,以及扩展性强。

IB的其他特点:基于Infiniband通信标准,核心特性是支持RDMA技术,可以实现在不经过CPU的情况下直接访问远程内存,减少CPU的开销和数据传输的时延,通常用于服务器互联及服务器连接存储的场景,能有效提高分布式计算的效率,提供40Gbps、56Gbps、100Gbps等高带宽。

IB/FC低时延交换机表现固然优秀,但其昂贵的造价以及运维困难的特点还是劝退了不少用户,部分客户更倾向使用支持RoCe、FCoE的以太网交换机进行平替。

可编程交换机

基于FPGA开发的交换机通常被称为可编程交换机,它们使用FPGA芯片来实现网络交换功能。这些交换机通常具有更高的灵活性和可编程性,可以根据需要进行配置和编程,以满足不同的网络需求和应用程序要求。

总结

来模拟一下报文转发情况,当普通数据流发送到设备port1时,ASIC芯片将直接通过匹配硬件表项来决定转发行为。而当信令、协议报文转发至port1时,ASIC芯片不能处理此类报文,将会把报文上送至CPU,由CPU统一处理, 当CPU处理过量报文时设备将不能稳定运行,所以在CPU设置处理上限及队列是软件设计的必要考虑。

更快的可能性

CPU+ASIC芯片的组合交换机可以满足绝大多数场景的需求,但在某些特定场景中,用户对于低时延交换机的要求是苛刻的,当前ASIC芯片多为商用(定制化设计),内部实现流程不透明;功能和算法在制造之前就被固定下来,转发查表架构固定,不能根据应用场景和具体科研需求进行更改,因此难以实现细分场景的极致需求。

IB/FC交换机

为实现极致低时延的网络诉求,IB及FC技术标准被定义。

共同点:

IB/FC交换机都可以执行Cut-through转发方式,即在接收到数据包的前半部分时就开始进行转发,而不必等到整个数据包接收完成。这种转发方式可以实现非常低的延迟,但可能会带来一些错误。

都采用专用的硬件转发引擎和硬件加速技术来减少时延。

FC的其他特点:基于光纤通道(FC)协议的低延时和低误码,支持点到点结构、环行拓扑结构和交换拓扑结构,通常提供4Gbps、8Gbps、16Gbps等带宽,适用于对性能要求较高的存储网络(SAN)应用场景。通过FC交换机将各个目标设备进行连接,以及FC交换机之间的级联,可以扩大存储区域网络的规模。 光纤通道传输速率高,延时低,以及扩展性强。

IB的其他特点:基于Infiniband通信标准,核心特性是支持RDMA技术,可以实现在不经过CPU的情况下直接访问远程内存,减少CPU的开销和数据传输的时延,通常用于服务器互联及服务器连接存储的场景,能有效提高分布式计算的效率,提供40Gbps、56Gbps、100Gbps等高带宽。

IB/FC低时延交换机表现固然优秀,但其昂贵的造价以及运维困难的特点还是劝退了不少用户,部分客户更倾向使用支持RoCe、FCoE的以太网交换机进行平替。

可编程交换机

基于FPGA开发的交换机通常被称为可编程交换机,它们使用FPGA芯片来实现网络交换功能。这些交换机通常具有更高的灵活性和可编程性,可以根据需要进行配置和编程,以满足不同的网络需求和应用程序要求。

总结

| 普通交换机 | IB交换机 | FC交换机 | 可编程交换机 | |

| 时延 | 高 | 低 | 低 | 取决于开发策略 |

| 稳定性 | 中 | 高 | 高 | 取决于开发策略 |

| 成本 | 低 | 高 | 高 | 规模越大成本越低 |

| 可管理性 | 简单 | 一般 | 困难 | 取决于开发策略 |