无线接入技术的发展,使得无线收发模块设计研究成为了一个重要研究方向。在众多无线通信技术中,IEEE 802.11b和IEEE 802.11g是两个重要的标准,它们分别工作在2.4 GHz的ISM频段。本文将重点介绍一种应用于IEEE 802.11b/g无线局域网标准的2.4 GHz ISM单片CMOS接收机射频前端设计。

接收机的设计需要考虑许多因素,如低成本、低功耗和高集成度等。为了满足这些要求,本文采用直接下变频接收机结构。这种结构具有许多优点,如降低电路复杂性、提高集成度等。此外,随着电路技术和工艺的进步,直接变频所固有的问题得到很大改善,如直流偏移和1/f闪烁噪声等。

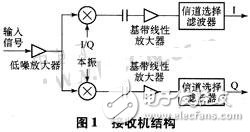

为了更好地实现接收机,本文详细介绍了其系统结构。接收机包括低噪声放大器、I/Q下变频器、去直流耦合电路、基带线性放大器和信道选择滤波器等模块。其中,低噪声放大器采用典型的差分Cascode结构,以提高共模抑制比和减少源极寄生电感影响。I/Q下变频器采用Gilbert单元有源双平衡混频器,以提高各端口之间的隔离度和线性度。

在电路实现过程中,本文还对低噪声放大器和I/Q下变频器进行了详细分析。为了提高低噪声放大器的性能,采用了键合电感以提高Q值和节省芯片面积,并采用了电流注入技术以提高线性度。对于I/Q下变频器,则分析了Gilbert单元的IIP3和噪声,并采用了电流注入技术来解决增益、线性度与噪声之间的矛盾。

通过优化电路参数和结构,本文成功实现了低噪声放大器和I/Q下变频器。在低噪声放大器方面,实现了0.84 dB的噪声系数、16 dB的增益和-15 dB的S11。在I/Q下变频器方面,实现了较高的线性度和较低的噪声。这些结果表明,本文提出的接收机射频前端设计具有较好的性能,能够满足IEEE 802.11b/g无线局域网标准的要求。

总之,本文介绍了一种应用于IEEE 802.11b/g无线局域网标准的2.4 GHz ISM单片CMOS接收机射频前端设计。通过对低噪声放大器和I/Q下变频器等关键模块的优化设计,成功实现了接收机射频前端。这种设计具有低成本、低功耗和高集成度等优点,能够满足现代无线通信的需求。

近年来,无线终端凭借低成本、低功耗和便于组网的优越性逐渐成为校园、机场、医院和家庭接人因特网的首选方案,无线接入技术得到迅速发展和广泛应用。无线收发模块的设计研究已成为一个重要研究方向。

本文介绍了一种应用于IEEE 802.11b/g无线局域网标准的2.4 GHz ISM单片CMOS接收机射频前端设计。IEEE 802.11b是目前市场上主流产品标准,而IEEE 802.11g则是IEEE 802.11系列的核心标准之一,它兼容另外两个核心标准IEEE 802.11a和IEEE802.11b,即同时支持IEEE 802.11a的OFDM(正交频分复用)和IEEE 802.11b的CCK(补码键控)编码的DSS(直接序列扩频)调制方式。本文中设计的接收机应用于DSS调制方式。

1 系统结构

考虑到低成本、低功耗和高集成度,针对IEEE802.11b/g本身宽信道带宽特性,本文采用直接下变频接收机结构。随着电路技术和工艺的进步,直接变频所固有的问题得到很大改善。尤其是直流偏移和1/f闪烁噪声问题,现在都能有效地降低它们的影响。

表1列出了近期设计的射频前端性能总结。

图1给出了接收机的系统结构,包括低噪声放大器、I/Q下变频器、去直流耦合电路、基带线性放大器和信道选择滤波器。

DSS标准包含11个2 MHz带宽的子信道,总的信道带宽为22 MHz。如果在保证误帧率在8×102情况下,要达到灵敏度为-80 dBm,那么,

kNF+RSNR=174 dBm-10log(22 MHz)-80 dBm=20.6 dBm

式中:KNF为噪声系数;RSNR为信噪比。

针对需要的FER,假设RSNR≈10 dB,再考虑到射频滤波器约2 dB损耗,接收机的要求低于8.6 dB。

标准还要求在接收信号-74 dBm时,具有40 dB的邻近信道抑制能力,鉴于此,接收机的输入1 dB压缩点要达到至少-30 dBm左右。

2 电路实现

2.1低噪声放大器

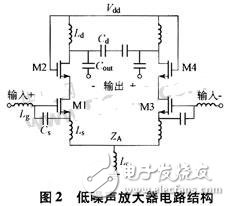

图2给出了低噪声放大器电路具体实现。电路采用典型的差分Cascode结构,增加对片上干扰抑制,减少源极寄生电感影响,另外,还能提高CMRR(共模抑制比)。不过,相对于单端输入单端输出,差分结构带来更大的功耗。

下面只分析放大器对称的左半部分,它是一个窄带Cascode结构低噪声放大器,这种结构能得到更好的噪声性能。Ls和Ld采用片上电感,Lc、Lg由键合电感实现。M1、M3是跨导晶体管,共栅连接的M2、M4提高输出输入之间的隔离,并减少M1、M3漏极电容Cgd的密勒效应。电容Cd、Cout和Ld调节输出匹配并起到与次级电路隔直的作用。

当然,除此之外,在优化电路时还应该考虑到电容Cs的影响,但式(1)、式(2)给出了各元件对电路性能的影响趋势,这点在设计电路时具有指导意义。

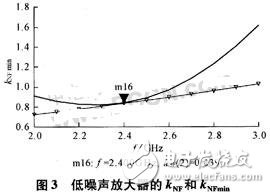

仔细选择器件参数,得到0.84 dB的噪声系数。从图3的仿真结果可看出,电路优化结果使kNF非常接近kNFmin。

用电感Le代替传统的尾电流源提高差分电路的共模抑制比,这样可以节省直流电压裕度。

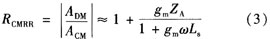

下式给出了CMRR(记为RCMRR)的参考公式:

式中:ZA为差分对管虚地点对地的阻抗。

电感采用键合电感,因为它有高Q值和节省芯片面积的优势。

仔细地在功耗与性能之间获取均衡,实现的低噪放噪声系数为0.84 dB,增益为16 dB,S11《-15 dB,直流电压1.8 V时电流为7.6 mA。

2.2 I/Q下变频器

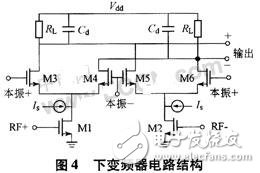

图4给出了I/Q正交下变频器的一路混频器。混频器的设计需要仔细选择每一个参数来平衡增益、线性度与噪声之间的矛盾。由于处于接收机射频信号最强处,往往混频器对线性度的要求很高。本文采用Gilbert单元有源双平衡混频器,具有较高的各端口之间的隔离度。跨导级晶体管源极直接接地,以提高混频器的线性度。电路中还采用电流注入技术,以降低混频器开关管的低频噪声,同时可以增大跨导级电流,改善线性度。

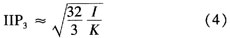

Gilbert单元的IIP3可以表示为:

式中:I和K分别是跨导电路的偏置电流和跨导参数。

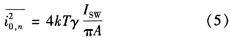

当本振信号是正弦波时,与开关对管有关的噪声为:

式中:A为本振信号的幅度;ISW为开关对管的偏置电流。

分析式(4)和式(5),需要增大跨导差分对管的偏置电流来提高混频器的线性度,同时又必须减小开关对管的偏置电流来降低开关噪声,因此,需要采用电流注入技术来解决二者之间的矛盾。