在有线通信领域,随着Gen AI网络速度从112G PAM4 SerDes升级到224G PAM4 SerDes,以太网芯片供应商如Broadcom、NVIDIA、Marvell和Cisco对超低抖动时钟解决方案的需求日益迫切。FemtoClock 3W凭借其卓越的性能,成为这些应用的理想选择。

在无线通信方面,FemtoClock 3W同样表现出色。其超低相位噪声特性使得它在毫米波无线射频应用中尤为重要。相位噪声直接影响数据速率和信噪比,FemtoClock 3W的低相位噪声设计确保了信号的纯净度和传输的稳定性。

FemtoClock 3W具备多项关键技术特性。首先,其RMS抖动在12kHz至20MHz区间低于25fs,满足224G PAM4 SerDes的严格时钟要求。其次,该产品配备3个DPLL和3个FOD,支持4个频域,灵活性极高。此外,FemtoClock 3W提供12个时钟输出,支持多种接口类型,如LVDS、HCSL和CML,覆盖广泛的频率范围。

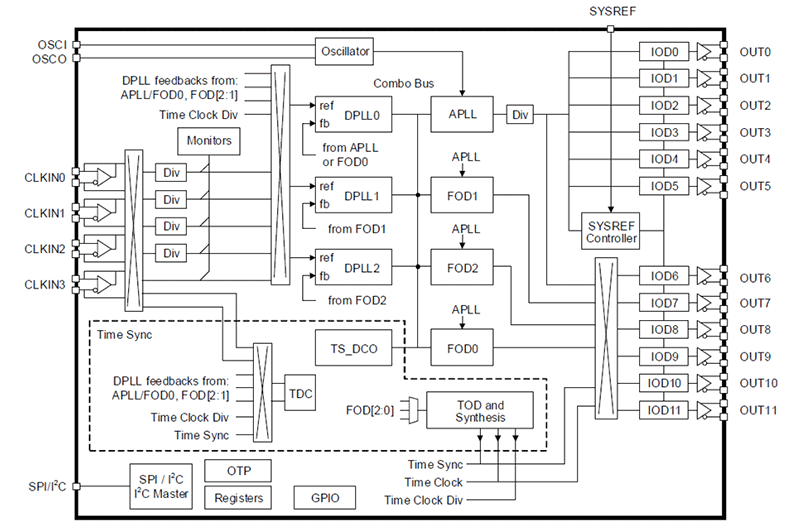

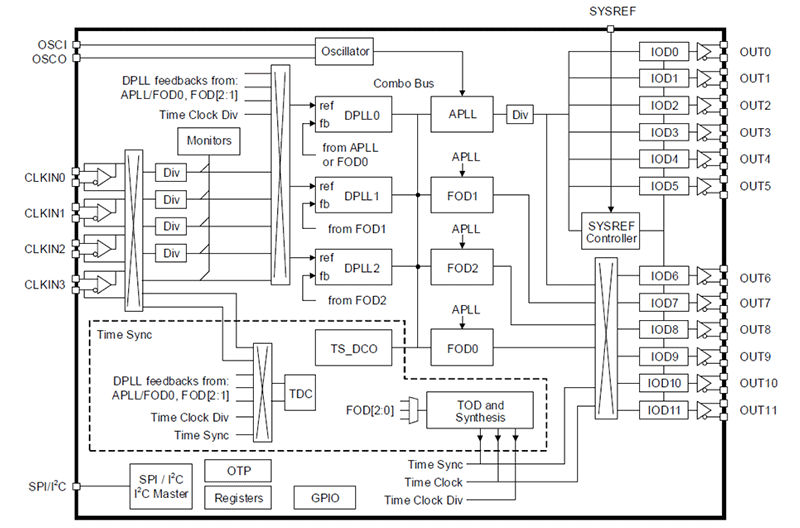

在架构设计上,FemtoClock 3W采用了先进的单芯片解决方案,集成了低相位噪声PLL、3DPLL、3小数输出分频器(FOD)、Combo总线和SysREF/JESD204B/C引擎,大大简化了系统设计,降低了复杂性和成本。

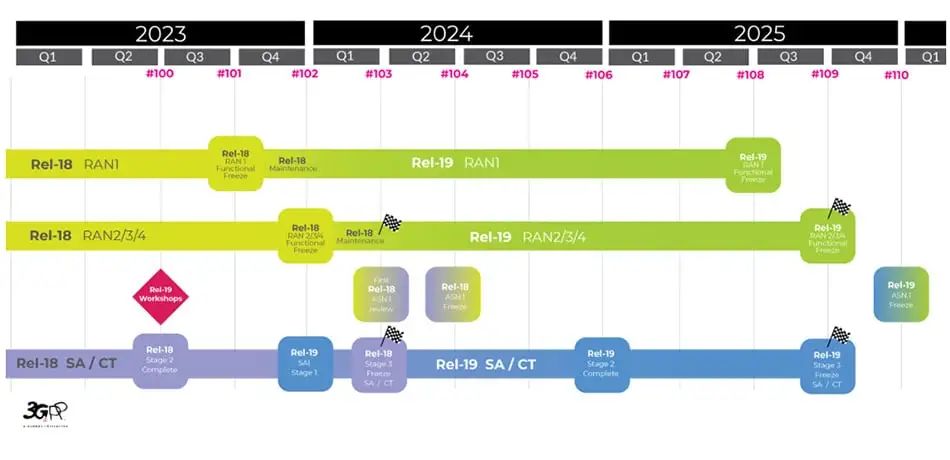

3GPP的Rel-19标准对“5G-Advanced”的定义至关重要,FemtoClock 3W完全符合这一标准,为未来的无线通信发展提供了强有力的支持。

总结而言,FemtoClock 3W以其超低相位噪声、高灵活性和先进架构,成为有线和无线通信领域的高性能时钟解决方案。无论是用于1.6T以太网交换机还是5G Advanced无线电单元,FemtoClock 3W都能提供稳定、可靠的时钟信号,助力下一代通信技术的发展。

如需进一步了解和评估FemtoClock 3W,可以访问瑞萨电子官网获取详细信息和评估套件。瑞萨技术论坛也提供在线技术支持,帮助用户解决在使用过程中遇到的问题。

Steve Lou,Principal Product Marketing Specialist

FemtoClock™ 3无线(3W)有两个主要应用:一个是有线通信中224G PAM SerDes参考时钟,另一个是无线通信中“5G Advanced”无线电单元或小型蜂窝。

由于最近GPU farm/AI节点的增加,Gen AI的所有网络速度都将从112G PAM4 Serdes转移到224G PAM4 SerDes(从 800G到1.6T)。多家以太网芯片供应商–Broadcom、Nvidia、Marvell和Cisco将很快在市场上推出以太网交换机芯片组解决方案,超低抖动时钟解决方案对他们来说变得至关重要。FemtoClock 3W(RC38312A)针对此应用。

关于RC38312A的更多信息您可复制以下链接至浏览器中打开查看:

HTTPS://www.renesas.cn/zh/products/clocks-timing/femtoclock-low-phase-noise-frequency-synthesizers/rc38312-femtoclock-3-wireless-3-channel-ultra-low-phase-noise-synchronizer-and-jitter-attenuator-12-outputs

图1 FemtoClock 3W(RC38312A)框图

RC38312A功能

▪ 超低相位噪声合成器,12kHz至20MHz区间的RMS jitter低于25fs RMS,在4MHz HPF条件下获得。

▪ 3个DPLL和3个FOD,支持4个频域。

▪ 支持JESD204B/C。

▪ 12个时钟输出,带独立整数分频器:

- 8:LVDS、HCSL(AC-LVPECL)或CML。

- 4:LVDS、HCSL(AC-LVPECL)或LVCMOS。

▪ 输出频率范围:

- CML:DC to 2.5GHz。

- LVDS或HCSL:DC to 1GHz。

- LVCOMS:DC to 250MHz。

▪ 4个差分或8个单端时钟输入。

▪ 可采用1.8V单电源供电。

▪ 功耗小于1.5W。

224G PAM4 SerDes的时钟要求

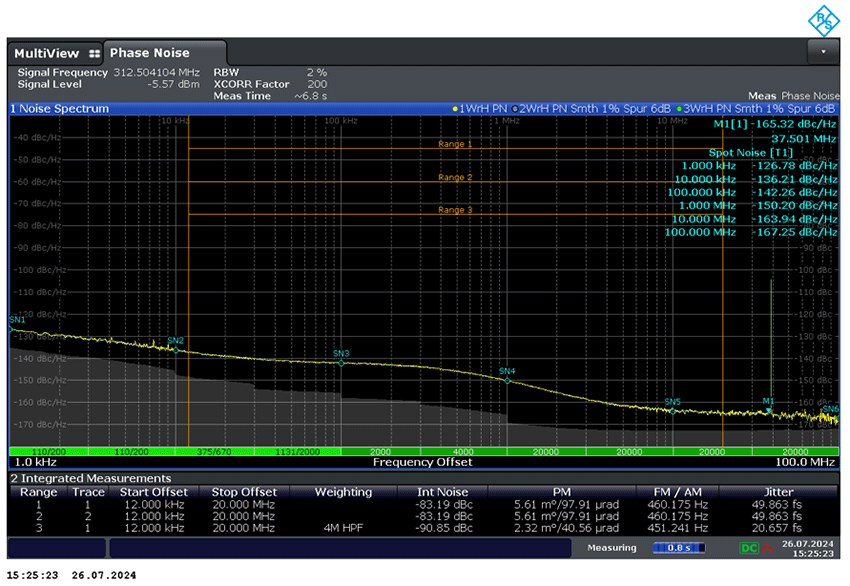

224G PAM4 SerDes的时钟要求非常严格,而FemtoClock 3W可以满足这些要求。224G PAM4的抖动要求低于25fs(12kHz至20MHz),在4MHz HPF条件下,FemtoClock 3W有充分的裕量满足该要求。

图2 显示20fs超低抖动的图表

支持有线和无线的时钟应用

RF频率合成器是当代先进的通信技术软件定义无线电系统中的重要组件。这些合成器的频谱纯净度至关重要,因为它直接影响可实现的最大数据速率和信噪特性。在RF应用中,频率合成器必须提供具有宽调谐范围和精确频率分辨率的高频时钟。要达到这些苛刻的性能标准,不仅需要有限的功耗和紧凑的芯片面积,还需要最小的杂散和相位噪声。

在实际的1024-QAM应用中,您可以了解抖动对图的影响。该协议仍然有助于减少错误。在商用SDR通信系统中,最佳时钟抖动性能是赢得顶级客户业务的关键。它会影响传输距离和数据速率。

高级架构

在4G无线电设计中,PLL系统使用外部VCXO提供低抖动时钟解决方案,JESD204B/C由PLL和FPGA实现。复杂性和成本是触发创新的关键因素,而同步使用的是另一个DPLL。它使定时系统带有同步DPLL、FPGA和带有外部VCXO的双环路抖动衰减器,总共4个组件。

在当代无线射频设计中,FemtoClock 3W进行了改进,包括支持低相位噪声PLL的单芯片、3DPLL、3小数输出分频器(FOD)、Combo总线、SysREF/JESD204B/C引擎和用于同步应用的TimeSync模块。

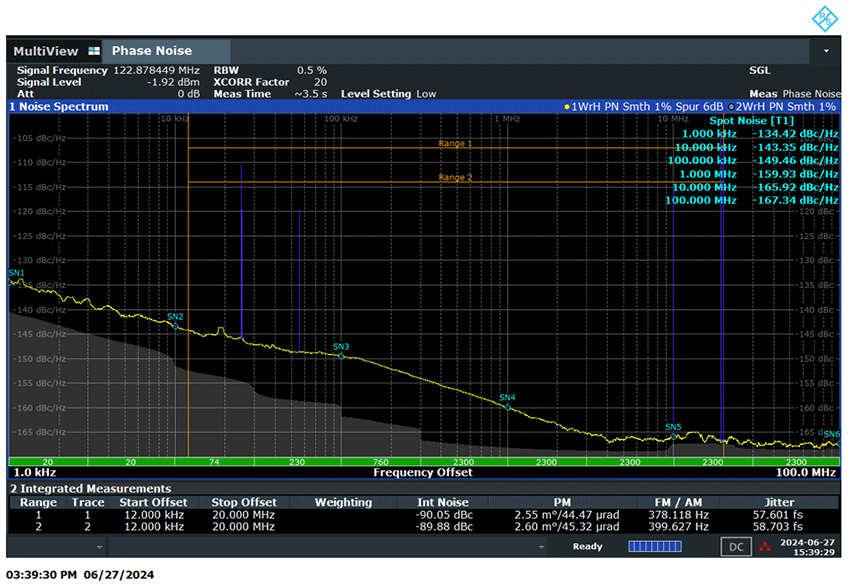

用于无线射频应用的超低相位噪声

如前所述,相位噪声对于毫米波无线射频应用至关重要。FemtoClock 3W基于BGA封装(低串扰)、低相位噪声PLL(Kronos PLL)、最高2.5GHz CML输出(高频输出通道)、相位调整和补偿而设计。

图3 122.88MHz的相位噪声曲线

3GPP时间表

Rel-19内容是在2025年12月的TSG(#102)上决定的,对于定义“5G-Advanced”的客户来说至关重要。

图4 3GPP时间表

资料来源:HTTPs://www.3gpp.org/specifications-technologies/releases/release-19

结论

FemtoClock 3W是瑞萨电子最新的PLL技术,支持无线和有线应用。采用单个1.8V电源,提供最低的功耗和超低相位抖动时钟输出。

FemtoClock 3W是无线射频单元和1.6T以太网交换机的224G PAM4 SerDes参考时钟的最佳时钟解决方案。

如需获取并评估FemtoClock 3W,请扫描下方二维码或复制链接至浏览器中打开查看:

RC38208A-EVK

https://www.renesas.cn/zh/products/clocks-timing/jitter-attenuators-frequency-translation/rc38208a-evk-femtoclock-3-wireless-ultra-low-phase-noise-synchronizer-and-jitter-attenuator-evaluation-kit

RC38312A-EVK

https://www.renesas.cn/zh/products/clocks-timing/jitter-attenuators-frequency-translation/rc38312a-evk-femtoclock-3-wireless-ultra-low-phase-noise-synchronizer-and-jitter-attenuator-evaluation-kit

需要技术支持?

如您在使用瑞萨MCU/MPU产品中有任何问题,可识别下方二维码或复制网址到浏览器中打开,进入瑞萨技术论坛寻找答案或获取在线技术支持。

https://community-ja.renesas.com/zh/forums-groups/mcu-mpu/