无线传感器网络MAC控制器是WSN协议栈中的关键模块,位于物理层和网络层之间。其主要功能是管理无线信道访问,确保传感器节点间通信的可靠性和高效性。本文提出的MAC控制器设计主要支持IEEE 802.15.4协议,能够适应20~250 kbps的数据传输速率。

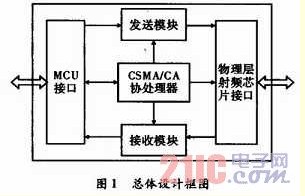

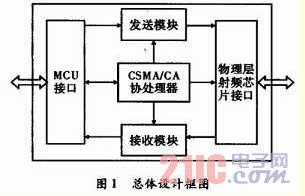

在设计过程中,我们采用了模块化设计方法,将MAC控制器分为发送模块、接收模块、CSMA/CA协处理器模块、PHY接口模块和MCU接口模块五个部分。以下是各个模块的具体实现:

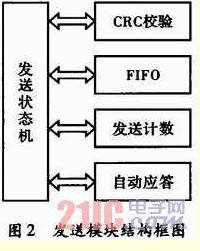

1. 发送模块:负责将上层协议提供的数据封装后通过PHY接口发送给PHY。发送状态机按照帧的格式将数据进行封装,并在数据前端添加前导序列和帧起始分隔符,在数据后端添加CRC校验值。发送模块包括发送FIFO缓存器、发送状态机、自动应答、发送计数器和CRC计算等子模块。

2. 接收模块:负责接收并识别符合IEEE 802.15.4协议格式的帧。接收状态机产生控制信号,将接收到的帧存储到接收缓存RxFIFO中。当接收到1Byte数据后,且Rx_fifowrite信号有效时,数据被写入到接收缓存RxFIFO。

3. CSMA/CA协处理器模块:是MAC的核心,控制接收和发送状态机协调半双工收发控制,并通过程序执行方式完成CSMA—CA算法。

4. PHY接口模块:负责将MAC控制器与物理层芯片(PHY)连接,实现数据在物理层与MAC层之间的交互。

5. MCU接口模块:负责将MAC控制器与微控制器(MCU)连接,实现控制逻辑与MCU之间的交互。

在仿真过程中,我们对MAC控制器进行了全面的测试,包括发送模块、接收模块和CSMA/CA算法等。仿真结果表明,该MAC控制器能够满足IEEE 802.15.4协议的要求,实现了高效、可靠的无线通信。

总之,本文提出了一种基于FPGA实现的无线传感器网络MAC控制器设计方法,通过模块化设计提高了系统的可扩展性和可维护性。该方法具有以下优点:

1. 设计简洁,易于实现; 2. 模块化设计,提高了系统的可维护性和可扩展性; 3. 仿真结果表明,该MAC控制器能够满足IEEE 802.15.4协议的要求,具有高效、可靠的通信能力。

随着WSN技术的不断发展,基于FPGA的MAC控制器设计方法有望在未来的无线通信领域发挥重要作用。

摘要

给出了一种由FPGA实现的无线传感器网络MAC控制器的设计方法,采用自顶向下的方法设计各个模块,并在QuartusII8.0完成了仿真,该控制器主要支持IEEE802.15.4协议。测试结果表明,该MAC控制器支持20~250 kbs数据传输速率,适应IEEE802.15.4协议要求。

媒体访问控制(Medium Access Control,MAC)协议处于无线传感器网络协议的物理层和网络层之间。用于在传感器节点间公平有效地共享通信媒介。它完成载波侦听多路访问(CSMA/CA)的信道存取、协议格式成帧或解帧、自动应答、系统多周期定时和帧校验等功能。

不同传感网络的应用有着不同MAC协议,其中IEEE802.15.4是最具代表性的协议。本文给出了用FPGA的控制逻辑来实现无线传感器网络MAC控制器的设计方法,并最终实现了符合IEEE802.15.4协议的控制器。

1 总体设计方案

无线传感器网络控制器的FPGA设计包括无线传感器网络MAC子层的FPGA设计、MAC子层与上层协议的接口设计以及与物理层(PHY)的接口设计。该无线传感器网络的总体结构设计如图1所示。

整个系统分为发送模块、接收模块、CSMA/CA协处理器模块、PHY接口模块和MCU接口模块5个部分。

发送模块和接收模块主要完成MAC帧的发送和接收功能,包括MAC帧的封装和解包,它直接提供了到外部物理层芯片(PHY)的串行接口。

CSMA/CA协处理器是MAC的核心,控制接收和发送状态机协调半双工收发控制,并且通过程序执行的方式完成CSMA—CA算法。

2 模块实现

2.1 MAC发送模块

发送模块可将上层协议提供的数据封装之后通过PHY接口发送给PHY。发送状态机按照帧的格式将数据进行封装,分别在数据的前端添加前导序列和帧起始分隔符以及在数据的后端添加CRC校验值,封装后的整个数据包以串行格式发送出去。

因此,发送部分的功能包括前导序列和帧起始分隔符插入、CRC计算、帧发送和自动应答等功能。

发送模块包括发送FIFO(First In First Out)缓存器模块(Tx_FIFO)、发送状态机模块(Tx_FSM)、自动应答模块(Tx_Ack)、发送计数器模块(Tx_Counter)和CRC计算模块(Tx_Crc)等5个子模块。其内部结构如图2所示。

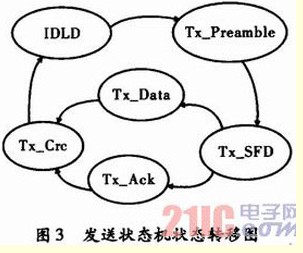

2.1.1 发送状态机Tx_FSM

Tx_FSM是整个发送模块的状态机,它是整个发送模块的核心,主要用于产生发送过程中各个模快的控制信号。发送的状态转移,如图3所示。TxCSP_en是来自MAC控制部分CSMA/CA协处理器的发送状态机控制信号。当TxCSP_en信号为高电平时,启动状态机,开始帧的发送过程。

(1)IDLE:初始状态。当发送状态机上电复位或者成功接收到数据包时,进入此状态。如果收到TxCSP_en信号时,开始数据发送过程,否则,保持此状态。

(2)Tx_Preamble:发送前导序列。当状态机将跳变到此状态,开始向数据线上发送符合特定组合的前导码序列。IEEE802.15.4协议的帧格式的前导序列是4 Byte O。

(3)Tx_SFD:发送帧起始分隔符。在这个状态下开始发送帧的帧起始符,IEEE802.15.4协议的帧格式的帧起始符为10100111。同时启动计数器,对该过程进行计数。

(4)Tx_Data:发送数据帧MPDU部分。这个状态下发送帧的有效数据,这个有效数据是来自上层。当发送完8位有效数据后,便产生读取FIFO缓存信号,从接收FIFO读取1Byte数据。

(5)Tx_Crc:发送数据包的CRC校验位。在这个状态下,发送帧的16位CRC校验码。

(6)Tx_Ack:发送应答状态。如果接收到的帧有应答要求,则启动该状态。

2.1.2 CRC校验电路

通过使用16位CRC串行校验来进行帧的差错校验,其中校验多项式采用。将要传送帧的MPDU通过CRC校验模块,便产生了16位CRC校验码。16位串行CRC校验电路如图4所示。

2.1.3 发送模块的仿真结果

图5是发送模块的仿真结果,Tx_clk是来自PHY接口的发送时钟,s_out是帧以串行方式发送。最先发送的前导序列码,接下来帧起始分隔符,再就是数据位,最后是CRC检验位。

2.2 MAC接收模块

接收模块的主要功能:接收并识别从串行数据线上输入的符合IEEE802.15.4协议格式的帧。如果协处理器RxCSP_en信号有效,则启动数据接收过程。通过接收状态机的控制,按帧格式顺序接收不同的数据域。当接收到1Byte数据后,且Rx_fifowrite信号有效时,数据被写入到接收缓存RxFIFO中。

接收状态机产生整个接收过程所需要的控制信号,在控制信号的作用下将接收到的帧存储到RxFIFO。接收部分的状态转移如图6所示。